Marco Ottavi Dimitris Gizopoulos Salvatore Pontarelli *Editors*

# Dependable Multicore Architectures at Nanoscale

Dependable Multicore Architectures at Nanoscale

Marco Ottavi · Dimitris Gizopoulos Salvatore Pontarelli Editors

# Dependable Multicore Architectures at Nanoscale

Editors

Marco Ottavi

Department of Electronic Engineering

University of Rome Tor Vergata

Rome

Italy

Dimitris Gizopoulos

Department of Informatics

and Telecommunications

National and Kapodistrian University

of Athens

Athens

Greece

Salvatore Pontarelli National Inter-University Consortium for Telecommunications (CNIT) Rome Italy

ISBN 978-3-319-54421-2 ISBN 978-3-319-54422-9 (eBook) DOI 10.1007/978-3-319-54422-9

Library of Congress Control Number: 2017943827

### © Springer International Publishing AG 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG

The registered company address is: Gewerbestrasse\_11, 6330 Cham, Switzerland

To my wife Fausta and my daughter Aurelia.

-Marco Ottavi

To my loves: my wife Georgia, my daughter Despina and my son Nikiforos.

—Dimitris Gizopoulos

To our Ph.D. advisor Adelio Salsano in memory of his dedication to work and his love for life.

-Salvatore Pontarelli and Marco Ottavi

### Foreword I

Dependable Multicore Architectures at Nanoscale is the latest and most exciting addition to the technical literature of fault-tolerant computing and dependable computer architecture.

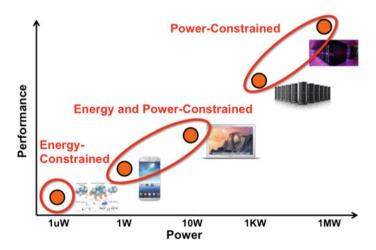

In the nanoscale manufacturing era in which correct circuit operation is jeopardized by multiple and sophisticated sources, or just be plain device unreliability, the understanding and the mitigation of circuits for dependable operation is commonly considered a mandatory design requirement. Dependability enhancement measures and mechanisms are widely utilized today in computing and electronic systems across the entire performance spectrum, from the high complexity of a super-computer down to handheld/embedded devices in mobile systems.

This edited volume captures an in-depth view of the state of the art in this ever-changing research and development domain. The chapters cover a broad treatment of the underlying challenges and related methodologies to deal with the increasing unreliability of state-of-the-art multicore architectures. In addition to capturing application-independent features, this book reports also contributions from major corporations and high-tech companies; the editors have also enlarged the scope of this book by involving researchers from major design companies to present views and expectations for future technical directions.

Dependable Multicore Architectures at Nanoscale serves the dual purposes of a textbook for students and active practitioners; the material here presented can serve as a reference as well as inspiration for advance treatment of theoretical and experimental studies, as found in today's dependable computing systems.

October 2016

Fabrizio Lombardi Northeastern University, Boston, USA

### Foreword II

Dependability of computing systems has been a major design concern since the early days of computing, with the goal of achieving high reliability and availability in the presence of unavoidable hardware and software faults. In recent years, the significance of computing systems' dependability has grown even more due to two major trends. The first is the relentless and continuous spread of computer-based controllers into almost every imaginable product and application, including critical and even life-critical ones. The second trend is the tremendous increase in the complexity of computing systems that now consist of many processing cores implemented using billions of devices. This trend is exacerbated by the advances in the sub-micron technology. These have, on one hand, allowed the vast increase in the number of devices per integrated circuit, but on the other hand, brought about new fault mechanisms and considerable process variations. All this has increased considerably the likelihood of a single device (out of a billion) to become defective during manufacturing or to fail (permanently or intermittently) during the system's lifetime.

This book provides a timely and updated survey of the main issues in the design and use of dependable contemporary multicore systems. It contains a comprehensive survey of the prevalent fault mechanisms in the current nanotechnology and describes in detail the available mitigation techniques to counter the effects of the potential faults.

Two unique features of this book must be highlighted. First, it includes an extensive set of actual application scenarios, illustrating the ways different faults can impact the behavior of these applications, and describing the corresponding mitigation techniques that can be applied. Second, it includes chapters contributed by researchers from three multicore design companies. These chapters provide practical perspectives, straight from the trenches, of the different facets of dependability.

x Foreword II

I highly recommend this book to researchers and practitioners in the vital, and continuously evolving, field of dependable computing systems.

October 2016 Israel Koren

University of Massachusetts, Amherst, USA

### Foreword III

I'm very pleased to write a foreword for this book which collects many significant and compelling contributions of the most active members of the MEDIAN community. I had the opportunity to work in the MEDIAN network of scientists and researchers and I believe that this book is the perfect way to crystallize and provide to a broader audience the discussions, the knowledge exchange, and the research results in the field of dependable multicore architectures achieved during the years in which the MEDIAN action was running. The book provides a solid background in the field of nanoscale reliability threats and possible mitigation strategies. These topics are discussed at different abstraction levels, without forgetting the interconnections and relationships between the various design layers. This makes this book a perfect tool for a reader who wants to approach the topic of dependability of current and next-generation systems. However, I believe that also experts of the field will appreciate this book for updating their knowledge and as a useful reference for their studies. The choice of describing the main threats and the most used mitigation solutions in specific application scenarios (use cases to the transportation, medical, and space) is one of the most intriguing reasons to read this book. At the same time, the vision provided by several scientists, researchers, and engineers working at the first line of the design of nanoscale systems provides a priceless instrument to know what will be the fundamental future trends in the field of dependable system design. This book can be used as a reference book and part of a reading list in a postgraduate course.

October 2016

Dhiraj Pradhan University of Bristol, Bristol, UK

### **Preface**

The increasing diversity, density, and complexity of electronic devices is enabling the so-called digital revolution with the evident pervasive presence of electronics in everybody's lives. The benefits of this ubiquitous presence are impressive and widespread: from the constant improvement of productivity in the workplace to the societal impact of a constantly connected and sharing community.

Whatever is the considered scenario, all this incredible progress has been relying on the assumption that the devices can be depended on in their application and for their purposes. The foundations for this assumption are based on a constant work behind the scenes of the technical and scientific community aimed at enhancing the dependability of the devices.

Dependability is a broad term that summarizes several aspects of a system, which typically include availability, reliability, maintainability, safety, and security. All these aspects define whether and how the system will behave according to several requirements which can have different levels of priority based on the specific application. In particular, availability measures the amount of time a system is readily operating, reliability measures the continuity of the correct service, maintainability shows the ability of the system of being repaired and/or modified, safety targets the avoidance of catastrophic consequences in the case of lack of service, and finally security targets the resilience of a systems to threats caused by malicious third parties.

There is an impressive amount of examples from technical literature and from the news about the dreadful consequences of the lack of dependability of an electronic system. Lack of dependability may have several negative consequences spreading from the loss of reputation of a manufacturer to the catastrophic loss of lives. Consider for example the automotive scenario, several cases of massive recalls were caused by issues in the electronic system: famously in one of such cases it was speculated that unintended acceleration causing loss of lives was to be ascribed to faults occurring in the drive-by-wire control modules.

Apart from the loss of lives, the economic impact of unreliable hardware must also be taken into account. Depending on the particular product and application domain, the costs associated to lack of dependability can be extremely high:

xiv

consider again the example, in the automotive domain, the costs caused by a massive recall of failing hardware, or in consumer electronics, the economic impact in loss of reputation for the manufacturer. Also, there are specific applications where the costs associated with replacing a failing hardware are just prohibitive: consider as an example the space industry where the replacement of failing hardware is all but impossible unless having to sustain huge costs.

A key step to obtaining dependable systems is at manufacturing. Manufacturing dependable digital electronic devices is a process that takes into account several aspects of the life and use of the designed device. At the manufacturing level, designers must take into account the new challenges introduced by the latest technology trends while at a system level the designer must include suitable approaches to counteract the potential occurrence of events that could lead to a non-dependable behavior.

Dependability and manufacturability are very related: from a temporal point of view, manufacturability deals with the cost-effectiveness of chips during production while dependability deals with the correctness of their operation later in the field. Manufacturability and dependability share common challenges and threats, have common objectives, and utilize common solutions regardless of the employment of chips in systems at the low end of performance and power (low-cost embedded systems or consumer electronics) or the high end of the performance (data centers, cloud computing facilities, or extremely powerful supercomputers).

It should be noted that aspects of manufacturability are very specific to the industrial process such as the cost of manufacturing and its accurate relation to yield. These aspects are not easily available to the academic community and therefore are not the focus of this book; instead, the book content is devoted to the actual physical threats and the mitigation techniques used in general and in particular application domains.

This book stems from the view of MEDIAN, a large network of researchers from academia and industry funded by COST¹ collaborating in the areas of manufacturability and dependability of multicore architectures and their deployment in different computing application domains. In particular, the focus is on multicore architectures.

The shift from increasing core clock frequencies to exploiting parallelism and multicore chip architectures has been the main design drive across all application domains in the electronics and computing industry. The introduction of multicore chips enabled a constant increase in delivered performance otherwise impossible to achieve in single-core designs. Multiple microprocessor cores from different instruction set architectures stay at the epicenter of such chips and are surrounded by memory cores of different technologies, sizes, and functionalities, as well as by

المنسارة للاستشارات

<sup>&</sup>lt;sup>1</sup>COST is the longest-running European framework supporting transnational cooperation among researchers, engineers, and scholars across Europe and is supported by the EU Framework Programme Horizon 2020.

Preface xv

peripheral controllers, special function cores, analog and mixed-signal cores, reconfigurable cores, etc.

The functionality as well as the complexity of multicore chips is unprecedented. This is the aggregate result of several technologies that emerged and matured together the last few decades: (a) manufacturing process now approaching the 10 nm regime and soon expected to go beyond, (b) sophisticated electronic design automation tools assisting and refining every step of the design process, and (c) new processor architectures across the entire spectrum of performance and power consumption.

The book is structured in three parts.

Part I (Chapter "Manufacturing Threats" to Chapter "Application Scenarios") describes the reliability threats of the latest nanoscale technologies and their modeling at different levels of abstraction of complex multicore systems, and shows the impact of these threats in several safety-critical scenarios.

Part II (Chapter "Manufacturing Solutions" to Chapter "Application-Specific Solutions") illustrates the possible mitigation strategies that can be applied to increase the dependability of complex systems. Also in this part, a specific chapter is dedicated to specific application scenarios, showing the relationship between the mitigation solutions and the characteristic of the environment in which the system will operate.

Part III (Chapter "Variation-Mitigation for Reliable, Dependable and Energy-Efficient Future System Design" to Chapter "Roadmap for On-Board Processing and Data Handling Systems in Space") collects the contributions of experts working in companies and public bodies (ARM, ESA, AMD, STMicroelectronics) providing their view about which are the most important and future trends in the field of design of dependable systems.

A detailed breakdown of contents of the chapters is the following.

Chapter "Manufacturing Threats" gives an overview of the reliability threats of the latest nanoscale generations of CMOS technology designs. First, a discussion on the process variability sources, and on the effect on circuit design and achievable performance is presented. After, the different wear-out physical effects such as Bias Temperature Instability (BTI), Hot Carrier Injection (HCI), Random Telegraph Noise (RTN), and Time-Dependent Dielectric Breakdown (TDDB) are analyzed. Finally, the chapter describes the physical phenomena provoking runtime variability effects such as voltage fluctuation and soft errors.

Chapter "Dependability Threats" provides an overview of fault/error models adopted in methodologies for dependability assessment, analysis, and mitigation, and presents an advanced reliability estimation technique for reliability estimation. Faults are categorized based on their applicability in the various abstraction layers. In particular, specific fault models have been included to take into account modern design trends such as FPGAs and NoCs. Furthermore, the chapter also gives special attention to modeling of aging and wear-out effects that arise during the operational life of the devices, causing either transient, intermittent, or permanent failures. The reliability estimation method is extended with the aim to provide a comprehensive system-level model able to consider multi-component architectures. The chapter

xvi Preface

ends with an overview of the relevant dependability metrics used in methodologies and techniques targeting dependability problems.

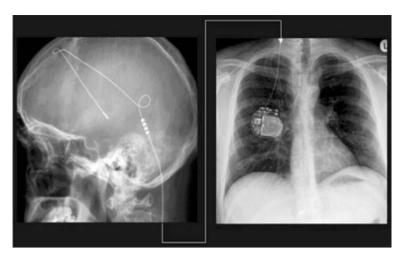

Chapter "Application Scenarios" shows several examples of how the faults occurring in modern technologies impact the system design in domains, such as automotive, railroad and transportation, air and space, and medical, where safety-critical and reliable operations are mandatory requirements. It addresses current practices deployed in these different domains and highlights the risks involved when the effects of the ever scaling technologies and related design techniques on system reliability are not properly taken into consideration. The chapter also discusses the growing interest problem of hardware security, which is a common challenge in all the domains.

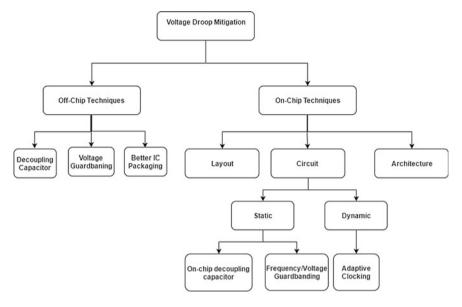

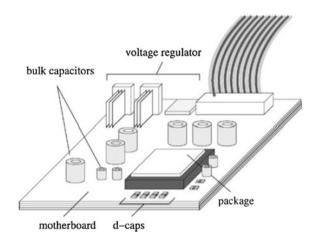

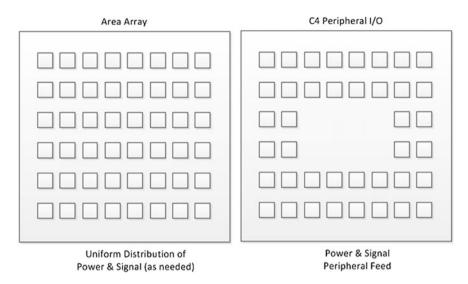

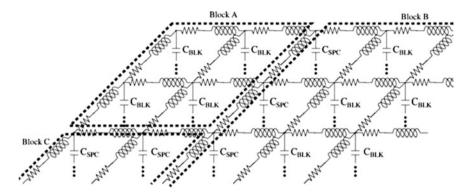

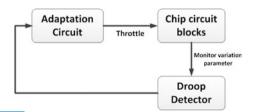

Chapter "Manufacturing Solutions" starts the second part of the book, where the design solution to the dependability threats discussed in the first part is presented. This chapter focuses on the threat described in Chapter "Manufacturing Threats" and presents the current available solution to mitigate faults. The presented solutions are applied at different design levels, depending on the specific threat to face and on the targeted dependability level. The chapter shows how to face some threat already during the process manufacturing, in which the used materials and the lithographic process are modified to limit the effects of process variability. Also, techniques based on layout design methodology are introduced. On n higher design level, several circuit level and RTL design level technologies are illustrated to different dependability threats (soft errors, voltage droop).

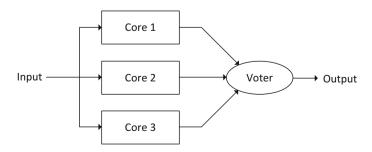

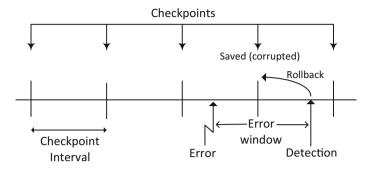

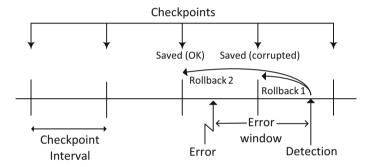

Chapter "Dependability Solutions" presents an overview of existing dependability solutions for processors and multicore processing systems. First, the existing techniques to protect processor cores both at the hardware and software level are discussed. Then the protection of the different memories that are present in a multicore is reviewed in the second section. Finally, the protection of the interconnections and an overview of specific Network on Chip dependability solutions are covered in the last section.

Chapter "Application-Specific Solutions" examines in detail some mitigation solutions applied in specific critical scenarios. It starts from the consideration presented in Chapter "Application Scenarios" considering a broader variety of application domains and their relation to dependability. The chapter shows how the specific design choices are strictly dependent on the application domain and how the selected solution can be different from each other.

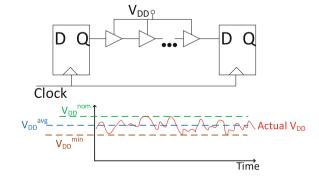

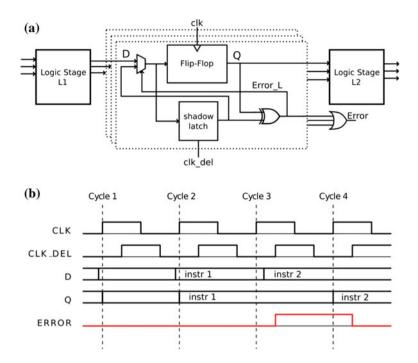

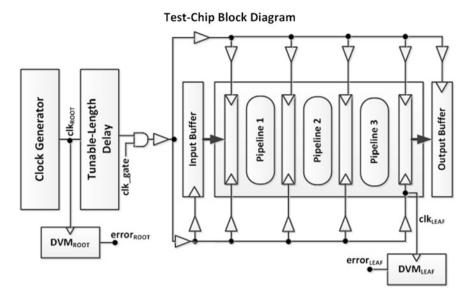

Chapter "Variation-Mitigation for Reliable, Dependable and Energy-Efficient Future System Design" is the first chapter of the third part of the book. The chapter provides the view from two ARM researchers about the major issues related to microprocessor dependability design. The chapter focuses on the issues related to process, voltage, and temperature (PVT) variations and the related mitigation strategies. An overview of the various sources of variation and the traditional approaches for variation-mitigation is presented. Afterward, several promising techniques for variation-mitigation are discussed. In particular, in situ aging monitors, error-resilient techniques, and adaptive clocking techniques are examinated. Furthermore, the chapter provides a detailed analysis of the Razor approach,

Preface xvii

showing the silicon measurement results from multiple industrial and academic demonstration systems that employ Razor.

Chapter "Design for Test and Test Equipment Roadmap" reports the experience of and the view of two researchers at AMD, another big player deeply involved in the design of next-generation multicore processors. The chapter topic is the resilience proportionality design, an interesting methodology to provide efficient and reliable systems. The chapter observes that chip design companies have to make difficult decisions about the exact dependability level that each product in their portfolio should provide and have few hints on which are the specific request and needs of customers and market segments. Therefore, the tradeoff between design cost, deployment cost, and the dependability level is a critical issue to address. The chapter proposes a resilience proportionality approach able to adapt a design to the dependability needs of a wide range of applications and hardware configurations.

Chapter "Resilience Proportionality—A Paradigm for Efficient and Reliable System Design" presents STMicroelectronics view and a roadmap for Design for test and test equipments. The current and future issues of VLSI test are examinated, highlighting how the exasperated operating conditions (very high temperature, severe mission profiles) and the limited confidence of the various adopted fault models (stuck-at, transition, and bridging) enlarge a progressive gap between the effective adherence of fault models to the actual defects present in IC. The chapter offers some perspective analysis on how these challenges can be faced and hopefully resolved. New synergies between DfT, test equipment, and test methods shall be proposed to highlight cause—effect relations. Special attention shall also be given to the sustainability of the costs of the proposed solution.

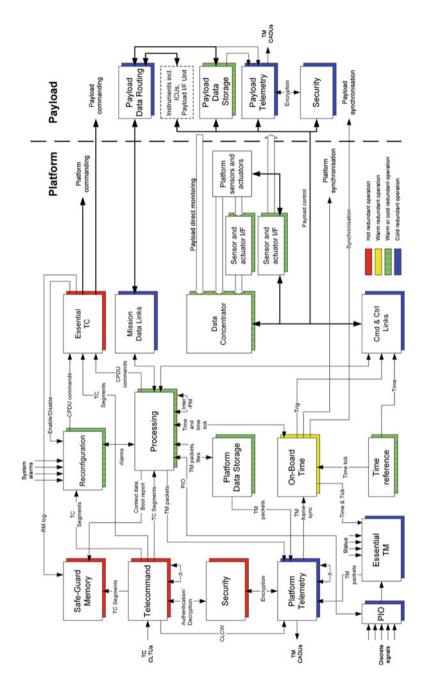

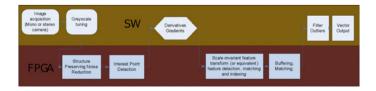

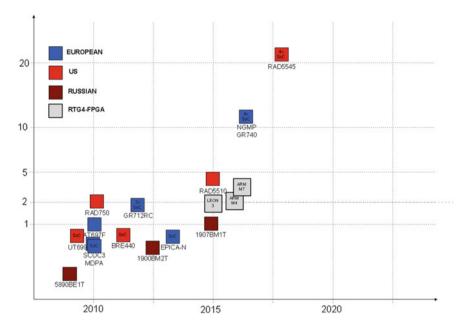

Chapter "Roadmap for On-Board Processing and Data Handling Systems in Space" gives the view of two European Space Agency (ESA) scientists about the evolution of on-board processing and data handling systems in the space environment. First, the chapter surveys the state of the art in this field and presents the description of a generic On-Board Computers and Data Systems Architecture. Afterward, the chapter continues identifying the historical path in the design of space system, starting from the old space microprocessors going to the current generation systems (multicore, FPGA, etc.), concluding with the expected future trends.

Dependable and manufacturable computing is a broad and intense research area concentrating major research effort worldwide from the circuit, architecture, and software communities. We believe that the snapshot of the area we deliver with this book reveals the tough challenges, the current directions, as well as the research opportunities in the near future. The forthcoming manufacturing technologies and the requirements of specific application domains will determine the advances in the field and the level of investment the industry will put on it.

xviii Preface

We sincerely thank the authors of the book chapters for devoting their time and energy in the corresponding chapters, Springer for publishing the book and COST framework for supporting the networking activities of MEDIAN.

Rome, Italy Athens, Greece Rome, Italy Marco Ottavi Dimitris Gizopoulos Salvatore Pontarelli

This book is based upon work from COST Action IC1103 ("Manufacturable and dependable multicore architectures at nanoscale (MEDIAN)"), supported by COST (European Cooperation in Science and Technology).

COST (European Cooperation in Science and Technology) is a funding agency for research and innovation networks. Our Actions help connect research initiatives across Europe and enable scientists to grow their ideas by sharing them with their peers. This boosts their research, career and innovation.

www.cost.eu

## **Contents**

| Part I Challenges                                                                                          |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Manufacturing Threats                                                                                      | 3   |

| Dependability ThreatsCristiana Bolchini, Maria K. Michael, Antonio Miele and Stelios Neophytou             | 37  |

| Application Scenarios                                                                                      | 93  |

| Part II Solutions                                                                                          |     |

| Manufacturing Solutions                                                                                    | 107 |

| Dependability Solutions                                                                                    | 155 |

| Application-Specific Solutions.  Viacheslav Izosimov, Antonis Paschalis, Pedro Reviriego and Hans Manhaeve | 189 |

| Part III State of the Art and Vision                                                                       |     |

| Variation-Mitigation for Reliable, Dependable and Energy-Efficient Future System Design                    | 219 |

| Design for Test and Test Equipment Roadmap                                                                 | 235 |

xx Contents

| Resilience Proportionality—A Paradigm for Efficient and Reliable |     |

|------------------------------------------------------------------|-----|

| System Design                                                    | 243 |

| Vilas Sridharan and Sudhanva Gurumurthi                          |     |

| Roadmap for On-Board Processing and Data Handling Systems in     |     |

| Space                                                            | 253 |

| Gianluca Furano and Alessandra Menicucci                         |     |

### **Contributors**

**Lorena Anghel** Grenoble Institute of Technology, Phelma, Grenoble Cedex, France

Davide Appello STMicroelectronics S.R.L, Agrate Brianza, MB, Italy

Cristiana Bolchini Politecnico di Milano, DEIB, Milano (MI), Italy

Shidhartha Das ARM Research, Cambridge, UK

Adrian Evans IROC Technologies, Grenoble, France

**Gianluca Furano** European Space Technology Centre—ESTEC—European Space Agency, Noordwjik, The Netherlands

**Sudhanva Gurumurthi** AMD Research, Advanced Micro Devices, Inc, Austin, TX, USA

Said Hamdioui Delft University of Technology, Delft, Netherlands

**Viacheslav Izosimov** Semcon Sweden AB, Linköping, Sweden; KTH Royal Institute of Technology, Stockholm, Sweden

Ben Kaczer Imec, Louvain, Belgium

Saman Kiamehr Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany

Juan A. Maestro Universidad Antonio de Nebrija, Madrid, Spain

Hans Manhaeve Ridgetop Europe, Bruges, Belgium

**Alessandra Menicucci** Faculteit Luchtvaart En Ruimtevaarttechniek, TUDelft, Delft, The Netherlands

Maria K. Michael University of Cyprus, Nicosia, Cyprus

Antonio Miele Politecnico di Milano, DEIB, Milano (MI), Italy

xxii Contributors

Stelios Neophytou University of Nicosia, Nicosia, Cyprus

Antonis Paschalis University of Athens, Athens, Greece

**Salvatore Pontarelli** Consorzio Nazionale Interuniversitario Per Le Telecomuni cazioni (CNIT), Rome, Italy

Pedro Reviriego Universidad Antonio de Nebrija, Madrid, Spain

**Vilas Sridharan** RAS Architecture, Advanced Micro Devices, Inc, Boxborough, MA, USA

Mehdi B. Tahoori Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany

# Part I Challenges

### **Manufacturing Threats**

Saman Kiamehr, Mehdi B. Tahoori and Lorena Anghel

**Abstract** This chapter introduces an overview of the main reliability threats of last nanoscale generations of CMOS technology designs. In particular, the chapter focuses on sources of process variability and their impact on circuit design and their performances, but also on the runtime variability such as voltage fluctuations as well soft errors. Further to that we go over the transistor aging provoked by different wear-out physical effects such as Bias Temperature Instability (BTI), Hot Carrier Injection (HCI), Random Telegraph Noise (RTN) and Time-Dependent Dielectric Breakdown (TDDB).

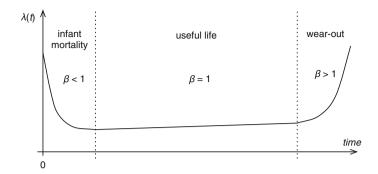

### 1 Reliability Issues

With aggressive downscaling of CMOS technology into deep nanometer, reliability has become a major issue [1]. In this section, the general sources of reliability issues in current technology nodes are briefly explained.

The sources of unreliability in current technology nodes can be categorized into three different categories: (i) variability issues, (ii) transient faults and soft errors (iii) permanent faults, all of them closely related to the fabrication process and to actual economical and physical difficulties to further improve the fabrication process [2], to the stochastic fluctuations of dopants in transistor channel and the thin oxide thickness [3] and to the intrinsic mechanisms of transistor and interconnect aging [4].

S. Kiamehr · M.B. Tahoori (🖂)

Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany

e-mail: mehdi.tahoori@kit.edu

S. Kiamehr

e-mail: kiamehr@kit.edu

L. Anghel

Grenoble Institute of Technology, Phelma, Grenoble Cedex, France

e-mail: lorena.anghel@imag.fr

© Springer International Publishing AG 2018

M. Ottavi et al. (eds.), *Dependable Multicore Architectures at Nanoscale*, DOI 10.1007/978-3-319-54422-9\_1

Due to variability, the devices/gates/circuits characteristics are different from the intended designed ones. The variability could be due to "time-zero" variation (process variation) or runtime variation such as voltage and temperature variations. Process variation is a natural device parameter variation which makes the properties of fabricated devices different from that of designed ones. In other words, due to process variation different similarly designed transistors/gates will perform (operate) with parametric differences after fabrication. Due to runtime variation, the transistors/gates properties will change (degrade) during the chip operational lifetime.

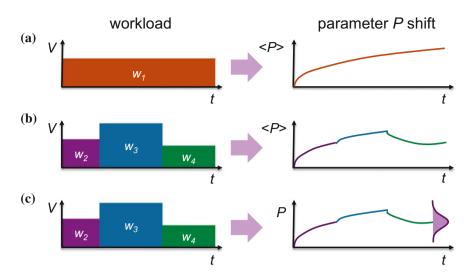

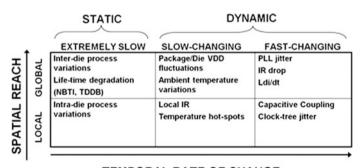

Runtime variations are routed in different sources such as voltage variation and temperature variation. The voltage and temperature variations are temporal or spatial according to the place of the transistor/gate and they depend on the workload, frequency and time of operation. Therefore, they cause variation on the properties of different transistors/gates at different locations of the circuit and at different time points during the chip operational lifetime.

Transistor aging is a source of runtime variations caused by different wear-out effects such as *Bias Temperature Instability* (BTI), *Hot Carrier Injection* (HCI) and soft *Time-Dependent Dielectric Breakdown* (soft TDDB), which in turn are dependent on process and runtime variations.

All these effects cause the threshold voltage of the transistors to increase and hence the switching delay of the gates that containing these transistors increases which can eventually lead to parametric timing failures if the delay of the circuit does not meet the timing constraints.

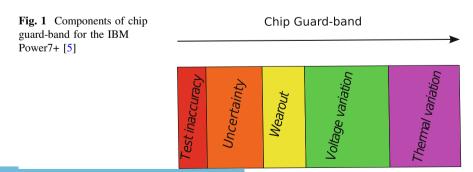

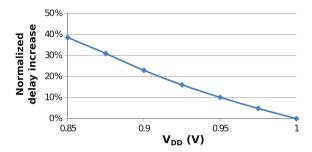

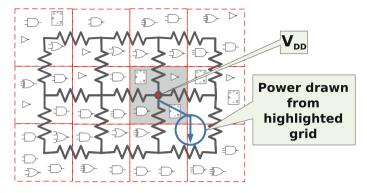

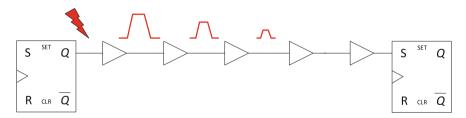

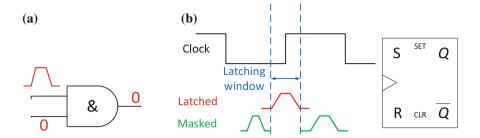

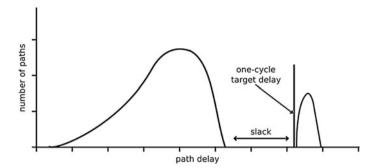

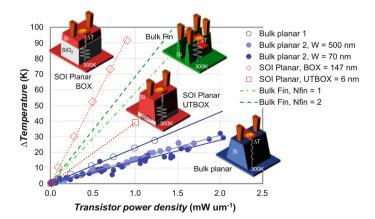

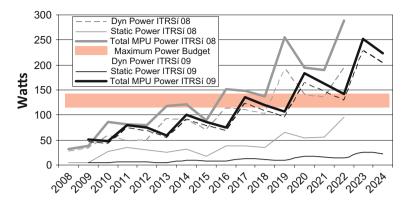

In order to deal with these sources of variation, traditional approaches consist in improving the technology process as much as possible, or to add guard-banding as a common approach at the design level. In the guard-banding approach, a timing margin is added to the designed clock cycle to guarantee the correct operation of the circuit during the operational lifetime. A pessimistic guard-banding leads to a performance loss and optimistic guard-banding results in a low reliability of the chip. Therefore, the required timing margin needs to be accurately predicted. Figure 1 shows the components of the required timing margin for IBM Power7+ processor [5]. As shown in this figure, the main components of the timing margin are uncertainty (e.g. global and local process variation), wearout (transistor aging) and voltage and thermal variations.

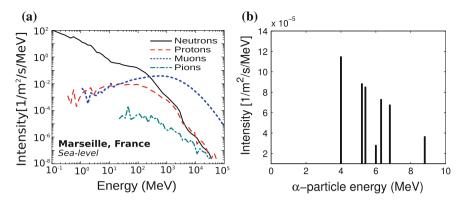

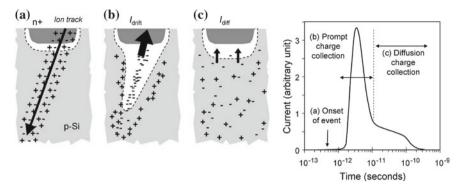

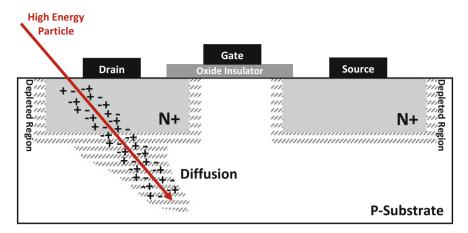

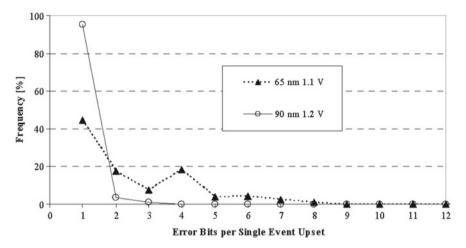

The other category of reliability issues is the transient soft errors caused by alpha particles generated by packaging materials and/or neutrons from cosmic particles. Transient soft errors do not cause a permanent degradation or fault and they lead to a transient computational error [6]. However, since its nature is random, the detection and correction of this type of errors can be very challenging [6]. The soft error can affect memory cell, sequential elements of the circuit but also combinational parts of the circuit. Traditionally, only single errors caused by *single event upsets* were considered as the target of detection and correction methods [7]. However, by continuous scaling of transistor dimensions, the probability that multiple nodes of the circuit are affected simultaneously by a strike [multi-bit transients in combinational circuits or multi-bit upsets in case of memories (MBU)] becomes larger which makes the detection and correction even more challenging.

Permanent fault is another important category of reliability issues which has been a concern since early days of electronic industry [6]. *Electromigration* (EM) is one of the most important types of permanent faults which can cause an interconnect disconnection due to the transport of material and it usually happens during runtime. EM is caused by the movement of ions in an interconnect due to the transfer of the momentum between the carriers and the atoms of the interconnect [8]. Permanent faults manifest themselves as logic errors (when properly activated by the circuit inputs) and may provoke catastrophic failures if their correction/decontamination is not handled.

Time-Dependent Dielectric Breakdown (TDDB) is also a major reliability issue which can lead to permanent fault [9]. The material of transistor gate oxide is degraded when a sufficiently high electric field is applied across the gate oxide which leads to an increase of its conductance. In case of a long-term application of electric field a conductive path may be formed through the gate oxide leading to an abrupt increase of gate leakage current. This issue is called hard TDDB and it becomes more severe as the gate oxide thickness becomes thinner due to the technology scaling.

In the following sections, some of the reliability issues which are targeted in this chapter will be explained in more detail.

### 2 Process Variation

The performance of a circuit is a function of its device characteristic and any variation in the characteristic of devices will lead to a deviation of the circuit performance from its intended designed value. This variation is called process variation and it can cause the circuit to fail if the performance of the circuit does not meet the constraint. Process variation can be categorized into two categories: (i) *Front-end variability* which is the variations caused by manufacturing process of the device (e.g. transistor length variation) and (ii) *Back-end variability* which is the variations caused by manufacturing process of the interconnect [10]. The contribution of these two types of variability is different for various types of reliability

concerns (e.g. timing variability or parametric yield) [10]. However, in terms of timing variability, front-end variability is dominant and its contribution in the total path delay is around 90% [11].

### 2.1 Sources of Front-End Variability

There are different sources of front-end variability, but we will explain the most important issues in the following.

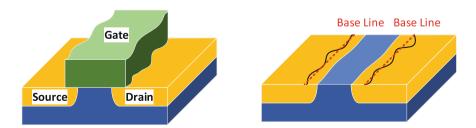

- Line Edge Roughness (LER): LER is the variation of the edge of the gate along its width which is due to the lithography variations [10] (see Fig. 2) or imperfections during photoresist removal [12]. LER impacts on different device characteristics such as the threshold voltage and the ratio between drive and subthreshold current [10, 13]. Chip manufacturers goal is to reduce this effect by applying corrections, such as optical proximity correction (OPC) or Phase Shift Masks (PSM). However, while shrinking down the gate, it is very challenging to reduce the deviations in the same ratio as the shrinking feature size.

- *Dielectric thickness variation*: The thickness of the dielectric between the gate and the channel has a large impact on the device characteristic such as the threshold voltage, the drive current and the leakage current [10]. This impact has significantly increased by the continued technology scaling (especially below 30 nm technology process with oxide thickness between 1 and 3 nm) and any variation in the thickness of dielectric will cause important variations in the device characteristic [14].

- Random Dopant Fluctuation (RDF): The dopant atoms are placed via ion implantation into the channel. The implantation step occurs such that the number and the location of dopant atoms in the channel are random. This phenomenon is called Random Dopant Fluctuation (RDF) which is a statistical variation of the number of implanted dopant and provokes variation of the threshold voltage of the transistor and thus the drive strength. The effect of RDF on the threshold voltage increases by the technology scaling since the number of dopant atoms in the channel decreases with the scaled dimensions [15]. RDF is considered the major source of mismatch for identical adjacent devices [13, 16].

Fig. 2 Line-edge roughness (LER) definition in the transistor

It is common to categorize variations in local and global variations. Global variations (or wafer-to-wafer variation) is mostly due to oxide thickness variations and RDF and affect transistors in the same way. Local variations are random mismatches between neighbour's transistors.

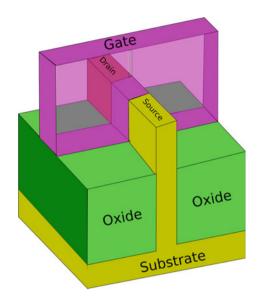

### 2.2 Process Variation in Emerging Technologies

The aim of new emerging devices such as FinFET technology is to decrease short channel effect as mentioned before in this section. However, they still suffer from some sources of variability. RDF is a major source of threshold voltage variation also for FinFET technology. This is due to the fact the threshold voltage of FinFET devices has a stronger linear dependence on the doping density compared to the conventional MOSFET devices [10]. The other source of threshold voltage variation in this technology is the thickness variation of the silicon fin [10, 17].

### 2.3 Process Variation Modelling

Since RDF is the major source of variation in advanced MOSFET and FinFET technologies [13, 16] and it significantly affects the threshold voltage of the transistor and the output capacitance of the gate, process variation is considered as the variation of the threshold voltage. A Gaussian (Normal) distribution is considered for the threshold voltage shift of transistors which has a mean value equal to zero and the standard deviation is obtained using Pelgrom model [10, 13, 18]:

$$\mu_{\Delta V_{\rm th}}^{PV} = 0 \tag{1}$$

$$\sigma_{\Delta V_{\text{th}}}^{PV} = \frac{A_{\Delta V_{\text{th}}}}{\sqrt{WL}} \tag{2}$$

where  $A_{\Delta V_{th}}$  is a technology dependent parameter, W is the width and L is the length of the transistor.

### 3 Transistor Aging

Transistor aging is one of the major sources of reliability issues in current technologies. The transistor switching delay is degraded over time due to the transistor aging which can eventually cause the circuit to fail if the timing constraint is not met. In this chapter, the focus is on the two major sources of transistor aging which

are BTI and HCI. The physical mechanism and modelling of these two effects will be described in more detail in the following sections.

### 3.1 Bias Temperature Instability (BTI)

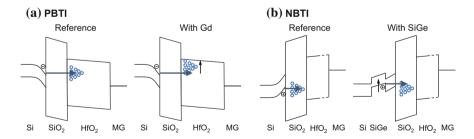

BTI is a wear-out phenomenon which gradually degrades the voltage threshold of a transistor and consequently the switching delay of the gate and further to that the circuit path delay. This degradation is monotonous over time. BTI consists of two similar phenomena: (i) *Negative BTI* (NBTI) affecting PMOS transistors and (ii) *Positive BTI* (PBTI) affecting NMOS transistors. NBTI was considered as an important reliability issue for a long time and PBTI was neglected due its small effect on NMOS transistors, however, by the introduction of high- $\kappa$  metal-gate technologies, PBTI becomes comparable to NBTI [19, 20]. NBTI degradation manifests as a degradation of all electrical parameters of a MOS transistor, under a negative VGS (for PMOS transistor) at relatively high temperatures. It is a static degradation phenomenon, as there is no current in the channel (VDS = 0 V). This degradation gets worse when increasing the temperature, but depends on the type of oxide (SiO<sub>2</sub>, SiON, HfO<sub>2</sub>, HfSiON) and its thickness [21, 22]. It is usual to quantify this degradation as an important increase of the threshold voltage and a direct current reduction.

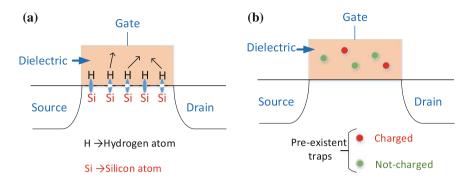

In general, there are two main models describing this phenomenon: (i) *Reaction–Diffusion* (RD) model [23–25] and (ii) *Trapping–Detrapping* (TD) model [26, 27]. According to both models, BTI consists of two phases:

- Stress Phase: the transistor is under NBTI (PBTI) stress if the gate source of the PMOS (NMOS) transistor is negatively (positively) biased at relatively high temperature. In other words, the transistor is under stress if it is ON. According to the RD model, in this phase, some of the Si–H bonds at the interface of the channel and the gate oxide are broken leading to the generation of interface traps (Reaction). This reaction is triggered by the carriers in the channel (electrons in NMOS and holes in PMOS). The reaction-generated species (hydrogen atoms or molecules) diffuse inside the gate oxide (diffusion) leading to the generation of traps inside the gate oxide. The generation of these traps at the interface of the channel/gate oxide and inside the gate oxide leads to an increase in the threshold voltage of the transistor. The RD mechanism is shown in Fig. 3a. On the other hand, based on the TD model, during the stress phase some pre-existent traps inside the gate oxide capture the charge which leads to an increase in the threshold voltage of the transistor (see Fig. 3b).

- **Recovery phase**: the transistor is in recovery phase if the gate source bias is removed, i.e. when the transistor is OFF. In this phase, according to the RD model, some of the generated traps are removed since some of the generated hydrogen atoms and molecules diffuse back especially for thin oxide thickness structures where the gate tunnel current is important. According to the TD

Fig. 3 BTI mechanisms: a Reaction–Diffusion (RD) mechanism. b Trapping–Detrapping (TD) mechanism

model, during this phase, some of the traps which captured the charge re-emit their charge. In general, the threshold voltage of the transistor decreases during the recovery phase, however, it cannot completely compensate the threshold voltage shift due to the stress phase.

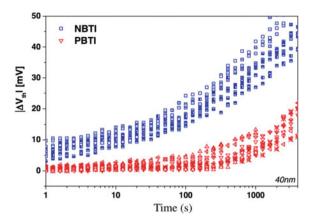

Similar behaviour occurs for NMOS transistor, and we call this phenomenon PBTI. In this case the carriers injected in the gate oxide under a positive VGS are the electrons. PBTI degradation is lower than NBTI, even for most advanced nodes [28, 29]. Next figure shows the evolution of the threshold voltage shift with the time for NMOS and PMOS transistors for 40 nm technology node, for the same input voltage constraint 2.5 V at 125°C [30].

The difference of behaviour between NBTI and PBTI is explained by the fact that holes are more efficient to generate defects inside the oxide and at the oxide interface than electrons that are injected in the channel by the gate tunnel current that occupy pre-existing defects in the dielectric.

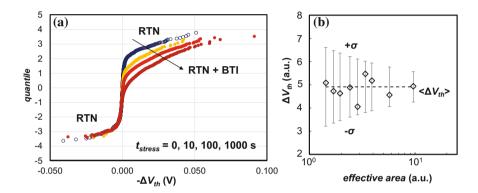

There is still a debate about the model which explains the BTI effect better (TD or RD). According to the literature, although the RD model is suitable to accurately predict the stress phase, it fails to cover the recovery phase [26]. It is observed that even after long time stress (1000 s), threshold voltage drops significantly after 1 s recovery (a very fast recovery) [31]. This fast recovery cannot be explained well by the RD model and it is well explained by TD model [32], however, the RD model is suitable to predict the long-term effect of BTI [26] (Fig. 4).

In previous technology nodes, the BTI effect on transistors was fairly deterministic for a particular workload condition (e.g. temperature and stress) [33]. However, by further downscaling of the transistor dimensions into deca-nanometer range, the number of defects per device decreases leading to a drastic increase in the time-dependent variability of BTI [34]. Thus, it is important to model the stochastic behaviour of BTI in advanced technology nodes. In the following we will explain two BTI models in more detail. One is a deterministic RD model and the other one is a stochastic atomistic trap-based model.

Fig. 4 Threshold voltage shift due to NBTI and PBTI for 40 nm technology node with voltage constraint 2.5 V at 125°C [30]

### 3.1.1 Deterministic RD Model

For the deterministic RD model we exploit the model proposed in [23, 24]. The model is proposed for NBTI effect, but since the mechanism of NBTI and PBTI are the same, we have used similar model to address the PBTI effect.

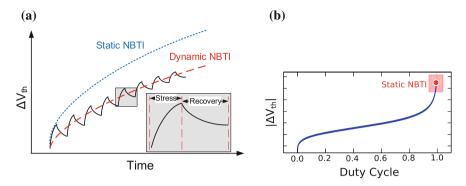

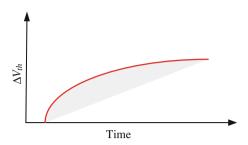

NBTI can be modelled for two different cases: (i) Static NBTI—in which the transistor is under constant stress, and, (ii) Dynamic NBTI—in which the transistor alternatively goes to stress (ON) and recovery (OFF) phases. The static NBTI is more severe compared to the dynamic one since the transistor has no time for recovery in the static NBTI (see Fig. 5a). The threshold voltage shift  $(\Delta V_{th})$  due to the static NBTI effect can be expressed by

$$\Delta V_{\text{th}}^{\text{static}} = A \left( (1+\delta)t_{\text{ox}} + \sqrt{C(t-t_0)} \right)^{2n} \tag{3}$$

$$A = \left(\frac{qt_{\rm ox}}{\varepsilon_{\rm ox}}\right) \sqrt[3]{K^2 C_{\rm ox} (V_{\rm GS} - V_{\rm th}) \left(\exp(\frac{E_{\rm ox}}{E_0})\right)^2}$$

(4)

where q is the electron charge,  $E_{ox}$  is the electric field of the gate oxide,  $C_{ox}$  is the oxide capacitance per area and n is a technology dependent factor which is either equal to 1/4 or 1/6. The other constants and coefficients are summarized in Table 1.

For dynamic NBTI, the  $\Delta V_{\text{th}}$  shift of each stress and recovery phases can be separately expressed by the following equations:

Stress:

$$\Delta V_{\text{th}} = \left(K_{\nu}(t-t_0)^1/2 + \sqrt[2n]{\Delta V_{\text{th0}}}\right)^{2n}$$

(5)

Recovery:

$$\Delta V_{\text{th}} = \Delta V_{\text{th}0} \left( 1 - \frac{2\xi_1 t_e + \sqrt{\xi_2 C(t - t_0)}}{2t_{\text{ox}} + \sqrt{Ct}} \right)$$

(6)

Fig. 5 a Static versus dynamic NBTI. b The dependency of dynamic NBTI to duty cycle

Table 1 RD model of NBTI-induced  $\Delta V_{\rm th}$

| NBTI-induced $\Delta V_{\text{th}}$                |                                                                                                    |                                                                                                                                                      |  |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Static                                             | $A((1+\delta)t_{\rm ox}+\sqrt{C(t_{\rm ox})})$                                                     | $A((1+\delta)t_{\rm ox} + \sqrt{C(t-t_0)}^{2n})$                                                                                                     |  |  |

| Dynamic                                            | Stress                                                                                             | $\left(K_{\nu}(t-t_0)^1/2+\sqrt[2n]{\Delta V_{\rm th0}}\right)^{2n}$                                                                                 |  |  |

|                                                    | Recovery                                                                                           | $\Delta V_{	ext{th0}} \left(1 - rac{2\xi_1 t_e + \sqrt{\xi_2 C(t-t_0)}}{2t_{ox} + \sqrt{Ct}} ight)$                                                 |  |  |

|                                                    | Long-term                                                                                          | $\left(\frac{\sqrt{K_v^2 \alpha T_{\rm clk}}}{1 - \beta_t^{1/2n}}\right)^{2n}$                                                                       |  |  |

| Constants and coefficients                         |                                                                                                    |                                                                                                                                                      |  |  |

| A                                                  | $\left(\frac{qt_{\rm ox}}{\varepsilon_{\rm ox}}\right)\sqrt[3]{K^2C_{ m ox}(V_{ m GS}-V_{ m ox})}$ | $\left(\frac{q_{t_{ox}}}{\varepsilon_{ox}}\right)\sqrt[3]{K^2C_{ox}(V_{GS}-V_{th})\left(\exp\left(\frac{E_{ox}}{E_0}\right)\right)^2}$               |  |  |

| $K_{\nu}$                                          | $\left(\frac{qt_{ m ox}}{\varepsilon_{ m ox}}\right)^3 K^2 C_{ m ox} (V_{ m GS} -$                 | $\left(\frac{qt_{\rm ox}}{\varepsilon_{\rm ox}}\right)^3 K^2 C_{\rm ox} (V_{\rm GS} - V_{\rm th}) \sqrt{C} \exp\left(\frac{2E_{\rm ox}}{E_0}\right)$ |  |  |

| $E_{\text{ox}}$                                    | $\frac{V_{\rm GS} - V_{\rm th}}{t_{\rm ox}}$                                                       | $\frac{V_{\mathrm{GS}} - V_{\mathrm{th}}}{t_{\mathrm{ov}}}$                                                                                          |  |  |

| C                                                  | $T_o^{-1} \cdot \exp(-E_a/kT)$                                                                     |                                                                                                                                                      |  |  |

| $t_e$                                              | if $t - t_0 > t_1$ otherwise                                                                       | $t_{ m ox} \ t_{ m ox} \sqrt{\frac{t-t_0}{t_1}} - \sqrt{\frac{\xi_2 C(t-t_0)}{2\xi_1}}$                                                              |  |  |

| $E_a(eV)$                                          | 0.49                                                                                               | 0.49                                                                                                                                                 |  |  |

| $E_0(V/nm)$                                        | 0.335                                                                                              | 0.335                                                                                                                                                |  |  |

| δ                                                  | 0.5                                                                                                | 0.5                                                                                                                                                  |  |  |

| $K(s^{-0.25} \cdot C^{-0.5} \cdot \text{nm}^{-2})$ | $8 \times 10^{4}$                                                                                  | $8 \times 10^4$                                                                                                                                      |  |  |

| $\xi_1$                                            | 0.9                                                                                                | 0.9                                                                                                                                                  |  |  |

| $\xi_2$                                            | 0.5                                                                                                | 0.5                                                                                                                                                  |  |  |

| $T_o$                                              | $10^{-8}$                                                                                          | 10-8                                                                                                                                                 |  |  |

where the constants and coefficients are described in Table 1. Equations 5 and 6 can be exploited to obtain the long-term dynamic NBTI-induced  $V_{th}$  shift when transistor undergoes alternate stress and recovery phases:

$$\Delta V_{\text{th}}^{\text{dynamic}} = \left(\frac{\sqrt{K_{\nu}^2 \alpha T_{\text{clk}}}}{1 - \beta_t^{1/2n}}\right)^{2n} \tag{7}$$

$$\beta_t = 1 - \frac{2\xi_1 t_e + \sqrt{\xi_2 C (1 - \alpha) T_{\text{clk}}}}{2t_{\text{ox}} + \sqrt{Ct}}$$

(8)

where  $T_{\rm clk}$  is the clock cycle.  $\alpha$  in this equation is the *Duty cycle* and defined as the ratio of the time in which transistor is under stress to the total time. NBTI-induced  $\Delta V_{\rm th}$  is a strong function of the duty cycle as shown in Fig. 5b. The dependence of duty cycle has been confirmed by many measurements performed by different industry teams, on different technology processes [35].

All the equations and related coefficients and constants are summarized in Table 1.

### 3.1.2 Stochastic Atomistic Trap-Based Model

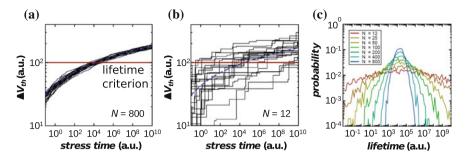

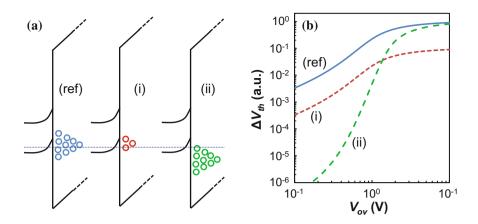

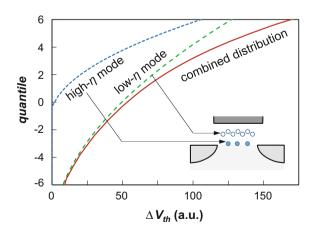

It is shown that a large portion of the BTI degradation and relaxation during the stress and the recovery phases is due to the charging and discharging of pre-existent gate oxide defects [36]. In previous technology nodes, the BTI effect on transistors was fairly deterministic for a particular workload condition (e.g. temperature and stress) due to the large number of defects in the device (see Fig. 6a). However, by further downscaling of the transistor dimensions into deca-nanometer range, the number of defects per device decreases leading to a drastic increase in the time-dependent variability of BTI [34] (see Fig. 6b). As a result, the lifetime of the device becomes also a *stochastic* value. Figure 6c shows the lifetime of the device for different technology nodes. As shown in this figure, the lifetime spread of smaller devices with lower number of defects is larger.

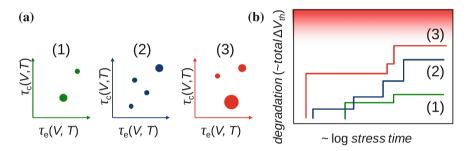

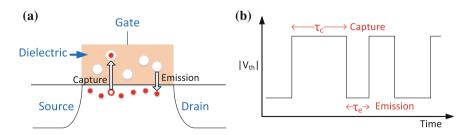

Therefore it is important to model the intrinsic variation of BTI. In this chapter, we consider the model proposed in [27, 37] for stochastic behaviour of BTI. In this model, each device is characterized by three different factors [27] (see Fig. 7).

- Number of defects (n)

- Defects capture time (τ<sub>c</sub>): it is defined as the time needed to charge a gate oxide defect during the stress phase.

- Defects emission time (τ<sub>e</sub>): it is defined as the time needed for the defect to re-emit its charge during the recovery phase.

By knowing these parameters for each device, the total BTI-induced  $\Delta V_{th}$  of each transistor can be calculated according to Fig. 7b. In this model the total number of defects is obtained from a Poisson distribution:

**Fig. 6** a BTI effect in large devices **b** stochastic behaviour of BTI in deeply scaled devices and **c** lifetime of devices for different technology nodes [37]

Fig. 7 a Parameters affecting BTI for three different devices **b** BTI-induced  $\Delta V_{\text{th}}$  for the three devices [27]

$$n = Poiss(N_T) \tag{9}$$

$$N_T \propto (L \cdot W)$$

(10)

where  $N_T$  is the mean number of charged (occupied) defects (traps). L and W are the length and width of the transistor. The effect of each occupied trap is obtained from an exponential distribution:

$$\Delta V_{\text{th}_i} = \text{Exp}(\eta) \tag{11}$$

$$\eta \propto 1/(L \cdot W) \tag{12}$$

where  $\eta$  is the average impact of individual defect on threshold voltage ( $\propto$  1/device area). An analytical description has been derived [27] for the total BTI  $\Delta V_{\rm th}$  cumulative distribution function as follows:

$$H_{\eta,N_T}(\Delta V_{\text{th}}) = \sum_{n=0}^{\infty} \frac{e^{-N_T} N_T^n}{n!} \left[ 1 - \frac{n}{n!} \Gamma(n, \frac{\Delta V_{\text{th}}}{\eta}) \right]$$

(13)

This formulation allows for an elegant parametrization of the distribution using the average number of defect  $N_T$  and the average impact per defect  $\eta$  which further describes the mean and the variance:

$$\mu_{\Lambda V_{th}} = \langle \Delta V_{th} \rangle = N_T \eta \tag{14}$$

$$\sigma_{\Delta V_{\rm th}}^2 = 2N_T \eta^2 \tag{15}$$

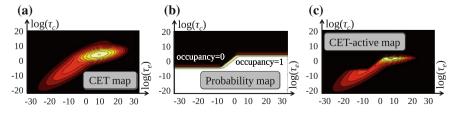

The average impact per defect  $\eta$  can be extracted from experiments [38]. The average number of defect  $N_T$  can be calculated using capture/emission time (CET) maps. CET map describes the probability density function of a broadly distributed defect capture and emission times and it is obtained from experimental data [39, 40] (see Fig. 8a). To build the complete CET map, an analytical two-component bivariate log-normal mixture distribution is used with a probability density of  $f_{\text{CET}}(\tau_c, \tau_e)$ . By integrating the CET map over the entire time domain the total defect density  $(n_T)$  and the mean number of available traps in each device  $(N_T^{\text{avv}})$  can be calculated as follows:

$$n_T = \iint f_{\text{CET}}(\tau_{\text{c}}, \tau_{\text{e}}) d\tau_{\text{c}} d\tau_{\text{e}}$$

(16)

$$N_T^{\text{avv}} = W \cdot L \cdot n_T \tag{17}$$

All of these available traps do not contribute on the total BTI-induced  $V_{\rm th}$  shift but those which are charged (occupied). The occupancy probability of each trap  $(P_{\rm occ})$  depends on the applied stress waveform (see Fig. 8b) and can be extracted by the following equation:

$$P_{\text{occ}} = \frac{1 - e^{-\frac{\pi}{f_{\text{rc}}}}}{1 - e^{-\frac{1}{f_{\text{cc}}}} \left(\frac{\pi}{f_{\text{cc}}} + \frac{1 - \alpha}{f_{\text{cc}}}\right)} \left(1 - e^{-t_{\text{stress}} \left(\frac{\pi}{f_{\text{cc}}} + \frac{1 - \alpha}{f_{\text{cc}}}\right)}\right)$$

(18)

where  $\alpha$  is the duty cycle (the ratio between the stress time to the total time), f is the frequency, and  $t_{\text{stress}}$  is the total time. Using this occupancy probability ( $P_{\text{occ}}$ ), the CET-active map can be obtained which shows the distribution of active traps (charged defects) according to the corresponding stress waveform (see Fig. 8c). By

Fig. 8 a CET map b occupancy probability map c CET-active map [34]

integrating the CET-active map over the entire time domain, the average number of defects  $(N_T)$  can be obtained by the following equations:

$$\rho = \frac{\iint_{\text{CET}}(\tau_c, \tau_e) P_{\text{occ}}(\tau_c, \tau_e, \alpha, t_{\text{stress}}, f) d\tau_c d\tau_e}{\iint_{f_{\text{CET}}}(\tau_c, \tau_e) d\tau_c d\tau_e}$$

(19)

$$N_T = \rho \cdot N_T^{\text{avv}} \tag{20}$$

where  $N_T$  is the average number of defects as a result of the applied stress waveform. This parameter is used in Eq. 13 to obtain the CDF of BTI-induced  $\Delta V_{\text{th}}$ .

### 3.1.3 Process Variation and Stochastic BTI: Are They Correlated?

Since both process variation and stochastic BTI can affect the threshold voltage of a transistor, it is important to consider the correlation of these two effects for the calculation of the total threshold voltage shift of the transistor considering both effects. According to [37, 41], there is no correlation between BTI-induced threshold voltage shift and process variation. However, there is a strong correlation between the standard deviation quantities of threshold voltage shift of these two variation sources since identical sources are responsible for process variation and stochastic BTI variability [42]. From measurements, independently of the technology [42], the correlation has been found to follow the empirical relation:

$$\sigma_{\Delta V_{\text{th}}}^2(t) = \frac{\mu_{\Delta V_{\text{th}}}}{B} \sigma_{V_{\text{thpv}}}^2 \tag{21}$$

$$B = 100 \,\mathrm{mV} \tag{22}$$

where B is a technology specific parameter. It is important to note that the variances are correlated here, the  $\Delta V_{\text{th}}$  and initial  $V_{\text{th}}$  are assumed not to be [37, 41].

Assessing the impact of degradation induced time-dependent variability of the  $V_{\text{th}}$  will be a difficult task in future technologies because of the uncertainty on the BTI critical parameters  $\eta$  and  $N_T$ . The correlation between process variation and stochastic BTI, however, gives a powerful predictive method for evaluating existing and future technologies. Combining Eq. (14) and (15) with Eq. (21),  $\eta$  can be directly derived from the initial process variation:

$$\eta = \frac{1}{2B} \sigma_{V_{\text{thpv}}}^2 \tag{23}$$

or combining with (Eq. 2)

$$\eta = \frac{A_{\Delta V_{\text{th}}}}{2B\sqrt{WL}} \tag{24}$$

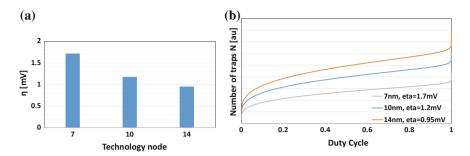

**Fig. 9** a  $\eta$  calculated using Eq. (24) for different FinFet technologies. **b** Average number of occupied traps as function of DF for different FinFET technologies calculated using Eqs. (18), (19) and (20)

Thus, for simulating future technologies,  $\eta$  is derived directly from the expected Pelgrom's mismatch parameter  $A_{\Delta V_{th}}$  [43–45] and  $N_T$  will be calculated using (Eq. 18), (Eq. 19) and (Eq. 20) with a CET map measured on poly silicon oxynitride (SiON) process technology. The scaling of oxide thickness  $T_{OX}$  and stress voltage is incorporated by using a power-law extrapolation for the overdrive electric field  $E_{OX}$  [46]. Here the  $V_{th}$  degradation is proportional to  $(E_{OX})^{\gamma}$ , where  $\gamma$  is the voltage acceleration which has a typical value of 3 [47]. Assuming there are no changes in the oxide or oxide quality the extrapolation towards more scaled nodes is done using the following relationship:

$$\frac{\langle \Delta V_{\text{th}_{\text{ref}}} \rangle}{\left( E_{\text{OX,ref}} \right)^{\gamma}} = \frac{\langle \Delta V_{\text{th}_{\text{sim}}} \rangle}{\left( E_{\text{OX,sim}} \right)^{\gamma}} \tag{25}$$

As shown in Fig. 9, values for  $\eta$  and  $N_T$  can be readily obtained when using the methodology described above.

### 3.2 Hot Carrier Injection (HCI)

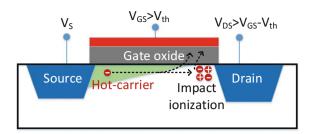

"Hot" carriers are referred to carriers which have a temperature much higher than the lattice temperature. When the transistor is in saturation mode, some of the carriers become "hot" due to the high lateral field and they gain enough energy to overcome channel/gate oxide potential barrier (channel hot carriers) [48]. These channel hot carriers may collide with the silicon atoms in the pinch-off region and generate electron—hole pairs due to the impact ionization. Some of the generated carriers may become "hot" and overcome channel/gate oxide potential barriers [48]. The second type of hot carriers is called avalanche hot carriers.

**Fig. 10** Hot carrier injection (HCI) physical mechanism

Both channel and avalanche hot carriers may be injected into the gate oxide and damage it generating traps inside the gate oxide or charge existing oxide traps. The gate oxide damage degrades the device characteristic such as the drain current and specially the threshold voltage of the transistor. This phenomenon is called *Hot Carrier Injection* (HCI) or *Channel Hot Carrier* (CHC) which is an important transistor aging issue in nanometer-technology nodes. The physical mechanism of HCI effect is depicted in Fig. 10. HCI describes degradation of the electrical parameters of a MOS transistor under a dynamic stress mode, as it occurs over the whole VDS/VGS range (note that BTI was present only under vertical electrical field with null VDS biasing). We can easily assume that HCI physical phenomenon is worst during the rise and fall bias of the transistors in a given gate.

HCI issue is observed as a critical issue in 80s [48] due to the high lateral electric filed in the technologies used in these period of time. However, from the mid-90s, the supply voltage started to decrease by the technology scaling to decrease the power consumption issue [49]. As a result the lateral electric field decreased and hence, the HCI effect became less by technology scaling. This trend has stopped in recent technology nodes, due to the fact that the supply voltage scaling is slowing down or stopping due to various reasons such as non-scalability of the threshold voltage and the subthreshold slope, signal-to-noise margin issue and process variation. Therefore, the lateral electric field started to increase and hence HCI again has become an important transistor aging issue [49].

HCI mainly affects NMOS transistors and its effect is negligible in PMOS transistors [50] since in the PMOS transistors fewer hot carriers are generated. The reason of this is twofold: (i) shorter mean free path of the holes and (ii) higher oxide barriers for holes.

### 3.2.1 HCI Model

In this section, we explain the HCI model that is used in the literature. As mentioned previously, the device characteristic such as threshold voltage and subthreshold slope is degraded due to the HCI effect. Here, the model of transistor  $V_{\rm th}$  shift as the main effect of HCI is explained (see Fig. 11). Hot carriers are generated

**Fig. 11** HCI-induced  $\Delta V_{\rm th}$  over time

during logic transition and hence the HCI induced  $V_{th}$  degradation is a function of switching frequency of the input signal [50, 51]:

$$\Delta V_{\rm th} = A_{\rm HCI} \times SW \times f \times e^{\frac{E_{\rm ox}}{E_1}} \times t^{0.5} \tag{26}$$

$$E_{\rm ox} = \frac{V_{\rm GS} - V_{\rm th}}{t_{\rm ox}} \tag{27}$$

where  $A_{\rm HCI}$  is a technology dependent constant, SW is the switching activity factor, and f is the clock frequency.  $V_{\rm th}$  and  $V_{\rm GS}$  are the threshold voltage and the gate source voltage of the transistor, respectively.  $t_{\rm ox}$  is the oxide thickness,  $E_1$  is a constant equal to  $0.8 \, \text{V/nm}$  [52] and t is the total time.

Moreover, it is shown that HCI effect depends on the temperature [49, 53]. Therefore, the HCI model of Eq. 26 is modified as follows:

$$\Delta V_{\rm th} = A_{\rm HCI} \times SW \times f \times e^{\frac{-E_a}{kT}} \times e^{\frac{E_{\rm ox}}{E_1}} \times t^{0.5}$$

(28)

where k is the Boltzmann constant and  $E_a$  the activation energy for the charge injection into the gate oxide.

### 3.3 Coupling Models for BTI and HCI Degradations

NBTI and HCI degradation are usually assessed independently one from the other. Their respective degradations are assumed to be additive. However, in [54] it is shown that these two phenomena are interacting and their contributions should be correlated. In fact, as the degradation rate is depending on the damage provoked by carriers, defects created during the two mechanisms are the same, only their respective localizations differ. It is shown through experiments, that the average total (BTI + HCI) degradation is largely overestimated up to a factor of 2 if a simple additive model is used. Thus correlated BTI and HCI models should be used during the evaluation of the degradation for a better accuracy.

## 3.4 Random Telegraph Noise (RTN)

Random Telegraph Noise (RTN) is an important source of runtime variation which is manifested as a low-frequency noise phenomenon and causes a temporal and random fluctuation of transistor electrical parameters, e.g. threshold voltage and drain current [55, 56]. It is shown that RTN is a serious reliability issue for image sensors [57], SRAM [58] and flash memories [59]. Variation due to RTN is increasing with the device downscaling and its effect exceeds process variation in 22 nm technology nodes [60, 61]. Therefore, RTN recently has become a reliability issue also for logic circuits specially for the ones performing under low supply voltage/low power applications [62, 63].

RTN is caused by the stochastic capture/trapping and emission/detrapping of mobile charged carriers into gate dielectric and therefore it shares some common mechanisms with BTI [56, 64, 65]. RTN mechanism and its effect on threshold voltage of transistor is shown in Fig. 12. A carrier in the channel might be captured by a trap in the oxide which leads to an increase in the threshold voltage value of the transistor. The captured carrier will be emitted back after a period of the time and thus the threshold voltage value decreases towards its original value. The capture/emission is a stochastic process and can be described by a two-state Markov chain [55, 66].

The power spectral density of the individual capture/emission process is Lorentzian power spectrum (slope =  $1/f^2$ ), however, the overall RTN effect is the superposition of many capture/emission events which leads to a 1/f noise in the frequency domain [56, 67].

#### 3.4.1 RTN Model

RTN has a stochastic behaviour and it is shown that its effect on the circuit leads to a long tail delay distribution [55]. Therefore, it is important to characterize and model the statistical behaviour of RTN. There have been many different models

Fig. 12 a Capture and emission of mobile carriers b threshold voltage fluctuation due to RTN

proposed in the literature; however, here we briefly describe a compact statistical model of the effect of RTN on the threshold voltage of transistor proposed in [68]. In this model, the statistics of number of traps  $(N_T)$  and the impact of each single trap on the threshold voltage of transistor  $(\Delta V_{\rm th}^{\rm ST})$  are modelled separately. Then, these two models are combined to obtain a complex model of overall impact of RTN on the threshold voltage of transistor. This model is described in more detail in the following.

## Number of Traps $(N_T)$

It is shown that the number of traps in the transistor follows a Poisson probability distribution [68]:

$$f_T(N_T; \lambda) = \frac{\lambda^{N_T} e^{-\lambda}}{N_T!}$$

(29)

where  $\lambda$  is the average number of traps which is a strong function of transistor dimensions and obtained from experimental measurements.

# Single-Trap effect on threshold voltage $\left(\Delta V_{ ext{th}}^{ ext{ST}}\right)$

Single-trap effect on the threshold voltage  $(\Delta V_{\rm th}^{\rm ST})$  has a long tail distribution and therefore it can be modelled by either an exponential distribution [69, 70] or a log-normal distribution [68, 71]. According to [68], a log-normal distribution leads to a better fit to the measured data:

$$f_l(\Delta V_{\text{th}}^{\text{ST}}; V_{\text{th0}}, \sigma_l) = \frac{e^{\frac{-(\ln \Delta V_{\text{th}}^{\text{ST}} - \ln \Delta V_{\text{th0}})^2}{2\sigma_l^2}}}{\sigma_l \Delta V_{\text{th}}^{\text{ST}} \sqrt{2\pi}}$$

(30)

$$V_{\text{th0}} = e^{\mu} \tag{31}$$

where  $\sigma_l$  is the log-normal shape parameter and  $\lambda$  is the mean of the distribution of  $\ln(\Delta V_{\rm th}^{\rm ST})$ .

## Overall effect of RTN on threshold voltage $\Delta V_{\rm th}$

In order to obtain the overall effect of RTN on threshold voltage  $(\Delta V_{\rm th})$ , the statistics of  $N_T$  and  $\Delta V_{\rm th}^{\rm ST}$  have to be combined into one comprehensive statistical model. For this purpose, it is assumed that the effects of individual traps on threshold voltage are independent which means that a simple superposition can be used to obtain the overall effects of all traps. Using superposition, the probability distribution function (PDF) of a system with n traps can be expressed as

$$f_{l,n}(\Delta V_{\text{th}}; V_{\text{th}0}, \sigma_l, n) = \int_{-\infty}^{\infty} f_{l,n}(\Delta V_{\text{th}} - u; V_{\text{th}0}, \sigma_l, n - 1) \times f_l(u; V_{\text{th}0}, \sigma_l) du \quad (32)$$

Then Eq. 29 can be used to obtain the contribution of the system with n traps into the total RTN effect as

$$a_n = P(N_T = n) = \frac{\lambda^n e^{-\lambda}}{n!}$$

(33)

Equations 32 and 33 can be combined to obtain the PDF of overall RTN effect as

$$f_{\rm c}(\Delta V_{\rm th}; V_{\rm th0}, \sigma_l, \lambda) = a_0 \delta_0(\Delta V_{\rm th}) + \sum_{i=1}^{\infty} a_i f_{l,n}(\Delta V_{\rm th}; V_{\rm th0}, \sigma_l, i)$$

(34)

and cumulative distribution function (CDF) of  $\Delta V_{th}$  can be expressed as

$$F_{c}(\Delta V_{\text{th}}; V_{\text{th0}}, \sigma_{l}, \lambda) = \int_{0}^{\Delta V_{\text{th}}} f_{c}(x; V_{\text{th0}}, \sigma_{l}, \lambda) dx$$

(35)

Concerning RTN, it is worth to note the following issues:

- Physically based 3D TCAD combined with Monte Carlo statistical simulation together with detailed experimental measures and circuit simulation is the present method to better and accurately understand the mechanisms leading to device degradation and the impact on circuit and gates degradations.

- RTN is highly correlated with local process variation, such as the random dopant fluctuation (RDF), line edge roughness (LER), and metal-gate granularity (MGG). Reference [72] shows that the impact on V<sub>th</sub> fluctuation is mostly due to RDF and MGG local variations.

- BTI degradation and impact on V<sub>th</sub> was compared with RTN impact and it was demonstrated a lack of correlation between these two effects [72].

- RTN has a serious impact on voltage sense amplifiers used for memory designs as the random fluctuation of PMOS drain currents can lead to read errors of stored data [73].

- FDSOI technology, alternatively used for very advanced geometries, shows less local process random variation than bulk technologies, similar RTN-induced variations of current amplitudes and threshold voltages were found [74]. This suggests that in future process nodes operating at lower voltages, RTN will be a major reliability issue.

# 3.5 Time-Dependent Dielectric Breakdown (TDDB)

Time-Dependent Dielectric Breakdown (TDDB) is an important transistor reliability concern where the quality of gate oxide is degraded over time in presence of high electric fields and it can eventually lead to severe failure in the gate oxide of

transistor and a huge leakage current. By technology downscaling, the gate oxide is scaled down; however, the supply voltage does not scale with the same trend. Therefore, the electric field over gate oxide increases and TDDB becomes more of a concern [75].

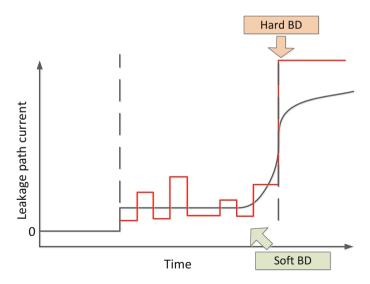

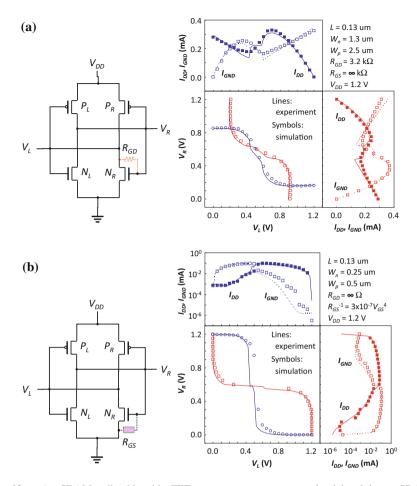

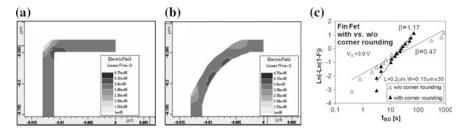

Generally, there are two types of TDDB called *soft breakdown (SBD)* and *hard break down (HBD)* based on the severity of the problem. In the presence of high electric fields, the channel carriers are trapped inside the oxide dielectric. By increasing the number of traps, they may form a resistive conduction path from gate to channel. In the beginning, the device is still functional; however, this leads to variations in the characteristics of transistors such as threshold voltage and current which is called SBD. The increase in the number of traps will cause the conduction path to become longer which eventually could lead to a catastrophic failure called HBD. When HBD happens, the device is not functional any more since a huge current is drawn from the gate to drain/source of the transistor. Figure 13 shows different phases of oxide breakdown and its impact on leakage path current of transistor [76].

The key reason of causing oxide degradation and eventually breakdown is trap generation. There are different models to explain the trap generation causing TDDB and a correct model is still debatable [9]. Three general models which is well discussed in literature are (1) *Anode Hole Injection* (AHI) model known also as 1/E model [77], (2) *thermo-chemical* model known also as E model [78] and (3) *Anode Hydrogen Release* (AHR) model [79].

Fig. 13 Time-dependent dielectric breakdown (TTDB) phases [76]

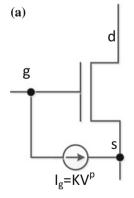

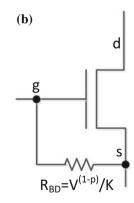

#### 3.5.1 SBD Model

As discussed before, due to SBD the leakage current of transistor increases which might impact on the circuit characteristics such as delay and energy. By technology scaling, the electric field over gate oxide increases which makes the SBD more pronounced [75]. Therefore, it is crucial to model the impact of SBD on the circuit characteristics. A very well-known model for SBD is voltage-dependent power-law gate oxide degradation model [80]. In this model, SBD-induced leakage current increase is modelled by a voltage-dependent current source or a voltage-dependent resistance between the gate and drain/source (see Fig. 14). The voltage-dependent resistance is obtained by the following equation [75]:

$$R_{\rm BD}(V) = V^{(1-p)}/K$$

(36)

where p represents the level oxide degradation and K reflects size of breakdown spot. These two parameters increase over time since the oxide degradation level increases. Extracting the values of K and p is very complicated since the device behaviour after SBD depends on many factors such as technology node, transistor type, oxide area, etc.

#### 3.5.2 HBD Model

Since after HBD the device is not functional any more, HBD normally modelled with a statistical parameter called *time-to-breakdown* ( $t_{\rm BD}$ ). Generally,  $t_{\rm BD}$  is modelled either with Weibull distribution [9] or log-normal distribution [81]. Here, we briefly explain the Weibull distribution model. The CDF of  $t_{\rm BD}$  can be described by:

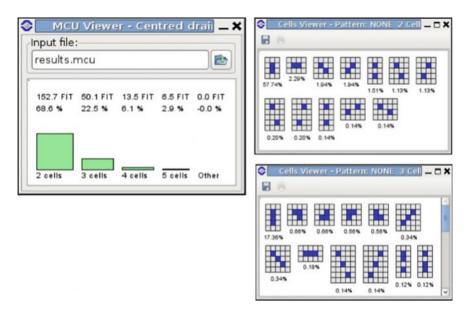

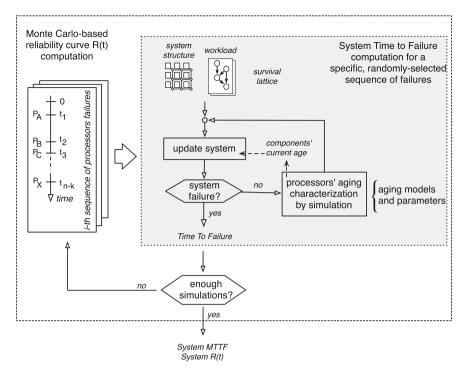

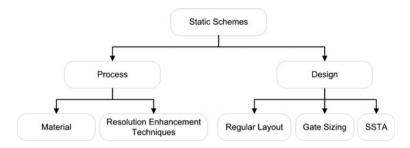

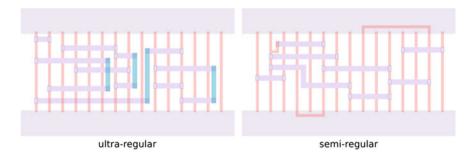

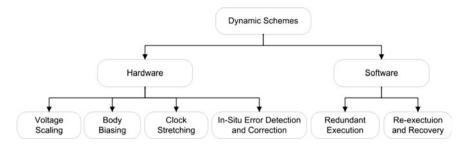

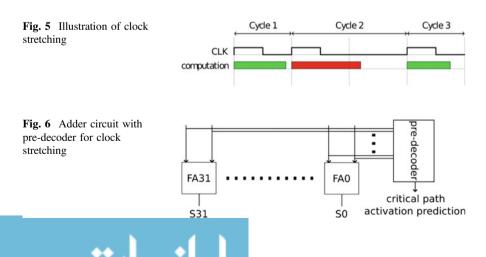

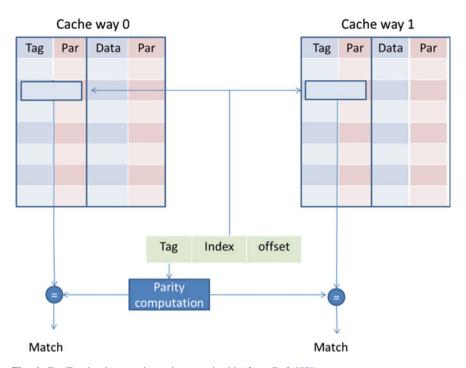

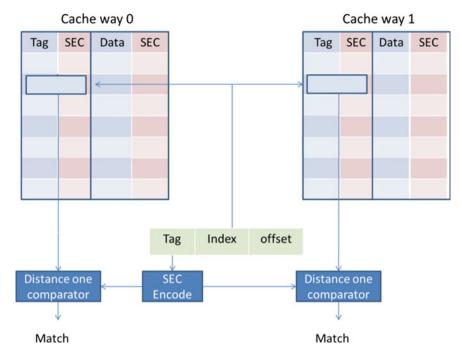

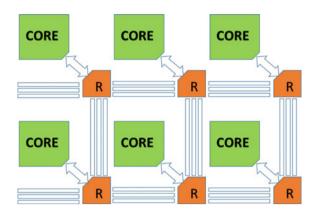

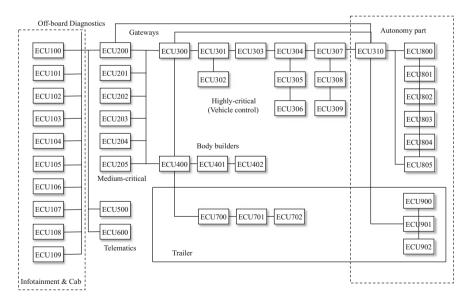

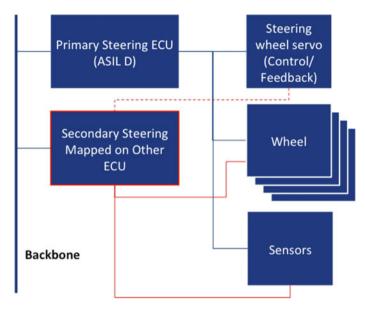

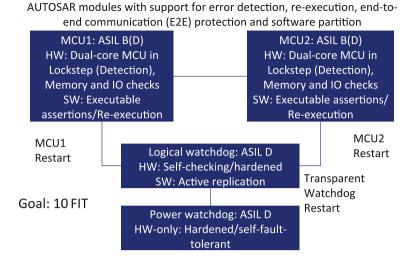

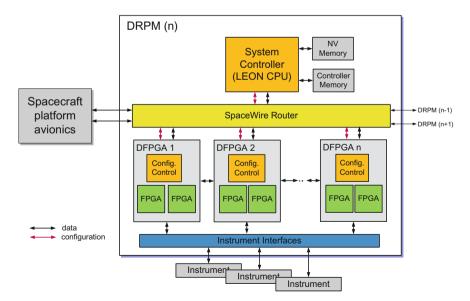

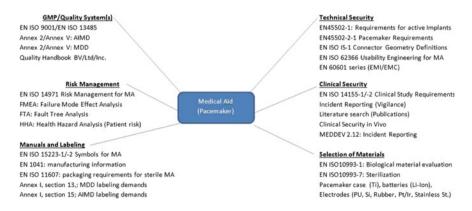

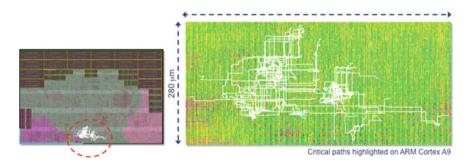

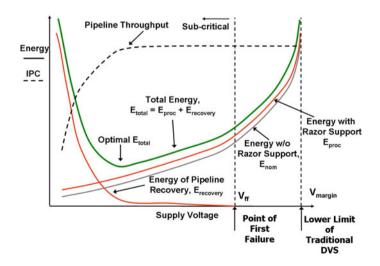

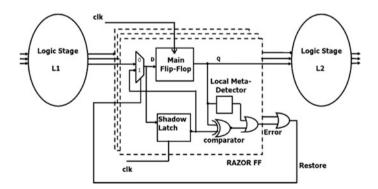

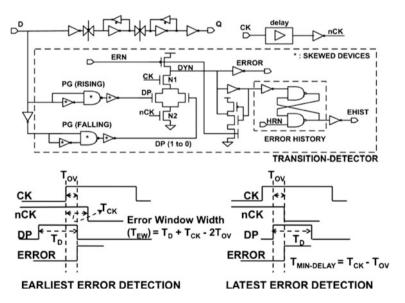

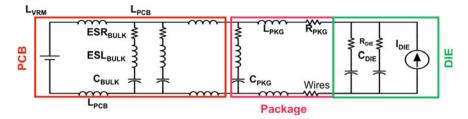

Fig. 14 Power-law SBD model a voltage-dependent current source b voltage-dependent resistance model [80]